SPS(Semiconductor Package Substrate)

微細な回路を持つ高密度基板に、半導体の電気信号をマザーボードに接続する半導体パッケージング工程の核心部品です。

高信頼性を要求する様々なモバイル機器と車載用に採用されています。

-

Overview

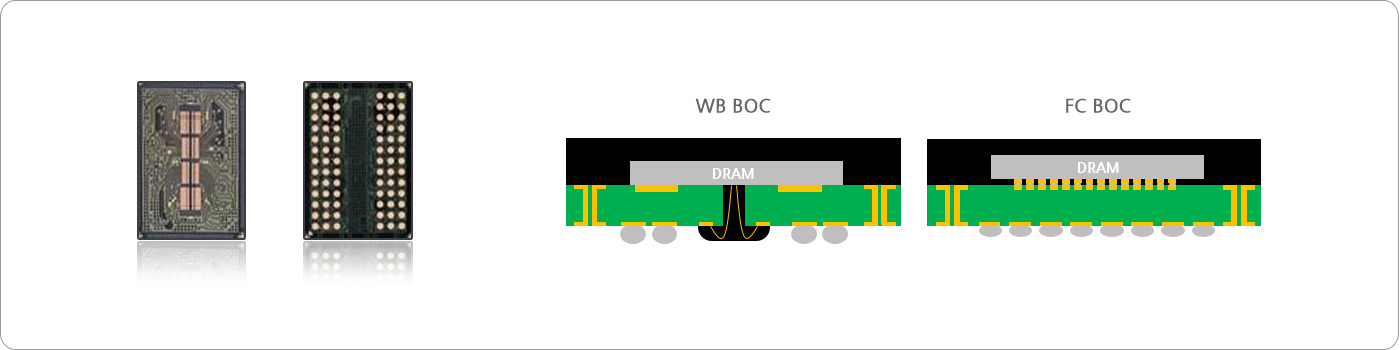

- BOC (Board on Chip)

- 過去DDR2からは、リードフレームではなくサブストレートを採用しててパッケージをしていましたが、この時、チップが中央スロットを通じて逆に(Face-down)実装されたことからBoard on Chipと名付けられました。また、ワイヤーボンディングパッドとソルダーボールが同Layerに位置することを特徴としています。

- 現在は、顧客企業のニーズに答えるため、従来の方式のままスロット経由でボンディングを施すWB BOC製品と、スロットなしでチップをバンプパッドに直接接続するFC BOC製品があります。

- Application

- PC/Server/CXL Memory Module DRAM

-

Core Technology

- Pattern Process : Tenting, MSAP

-

Specifications

DDR4 DDR5 Layer 2L 2L Thickness 258~265µm 180~220µm Process Tenting Tenting, MSAP Trace Pitch (Width/Space) 55pt (25/30) 50pt (25/25) PSR AUS308 ← Surface Finish W/B Ni/Au ← F/C OSP ← -

Product Image